## LMH6628

## Dual Wideband, Low Noise, Voltage Feedback Op Amp

## **General Description**

The National LMH6628 is a high speed dual op amp that offers a traditional voltage feedback topology featuring unity gain stability and slew enhanced circuitry. The LMH6628's low noise and very low harmonic distortion combine to form a wide dynamic range op amp that operates from a single (5V to 12V) or dual (±5V) power supply.

Each of the LMH6628's closely matched channels provides a 300MHz unity gain bandwidth and low input voltage noise density (2nV/  $\sqrt{\text{Hz}}$ ). Low 2nd/3rd harmonic distortion (–65/–74dBc at 10MHz) make the LMH6628 a perfect wide dynamic range amplifier for matched I/Q channels.

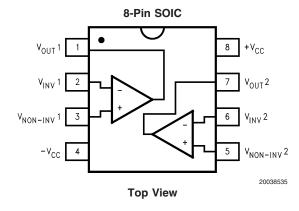

With its fast and accurate settling (12ns to 0.1%), the LMH6628 is also an excellent choice for wide dynamic range, anti-aliasing filters to buffer the inputs of hi resolution analog-to-digital converters. Combining the LMH6628's two tightly matched amplifiers in a single 8-pin SOIC package reduces cost and board space for many composite amplifier applications such as active filters, differential line drivers/receivers, fast peak detectors and instrumentation amplifiers.

The LMH6628 is fabricated using National's VIP10™ complimentary bipolar process.

To reduce design times and assist in board layout, the LMH6628 is supported by an evaluation board (CLC730036).

#### **Features**

■ Wide unity gain bandwidth: 300MHz

■ Low noise: 2nV/ √Hz

■ Low Distortion: -65/-74dBc (10MHz)

■ Settling time: 12ns to 0.1%

■ Wide supply voltage range: ±2.5V to ±6V

High output current: ±85mAImproved replacement for CLC428

## **Applications**

■ High speed dual op amp

■ Low noise integrators

■ Low noise active filters

■ Driver/receiver for transmission systems

High speed detectors

■ I/Q channel amplifiers

## **Connection Diagram**

## **Inverting Frequency Response**

20038515

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance (Note 4)

$\begin{array}{ccc} \text{Human Body Model} & 2 \text{kV} \\ \text{Machine Model} & 200 \text{V} \\ \text{Supply Voltage} & 13.5 \\ \text{Short Circuit Current} & (\text{Note 3}) \\ \text{Common-Mode Input Voltage} & \text{V}^+ \cdot \text{V}^- \\ \text{Differential Input Voltage} & \text{V}^+ \cdot \text{V}^- \end{array}$

Maximum Junction Temperature  $+150^{\circ}$ C Storage Temperature Range  $-65^{\circ}$ C to  $+150^{\circ}$ C Lead Temperature (soldering 10 sec)  $+300^{\circ}$ C

## **Operating Ratings** (Note 1)

Thermal Resistance (Note 5)

$\begin{array}{ccc} \text{Package} & (\theta_{\text{JC}}) & (\theta_{\text{JA}}) \\ \text{SOIC} & 65^{\circ}\text{C/W} & 145^{\circ}\text{C/W} \\ \text{Temperature Range} & -40^{\circ}\text{C to } +85^{\circ}\text{C} \\ \text{Nominal Supply Voltage} & \pm 2.5\text{V to } \pm 6\text{V} \\ \end{array}$

#### **Electrical Characteristics** (Note 2)

$V_{CC}$  = ±5V,  $A_V$  = +2V/V,  $R_F$  = 100 $\Omega$ ,  $R_G$  = 100 $\Omega$ ,  $R_L$  = 100 $\Omega$ ; unless otherwise specified. **Boldface** limits apply at the temperature extremes.

| Symbol           | Parameter                           | Conditions                          | Min               | Тур | Max               | Units   |

|------------------|-------------------------------------|-------------------------------------|-------------------|-----|-------------------|---------|

| Frequency        | Domain Response                     |                                     |                   |     |                   |         |

| GB               | Gain Bandwidth Product              | $V_O < 0.5V_{PP}$                   |                   | 200 |                   | MHz     |

| SSBW             | -3dB Bandwidth, A <sub>V</sub> = +1 | $V_O < 0.5V_{PP}$                   | 180               | 300 |                   | MHz     |

| SSBW             | -3dB Bandwidth, A <sub>V</sub> = +2 | $V_O < 0.5V_{PP}$                   |                   | 100 |                   | MHz     |

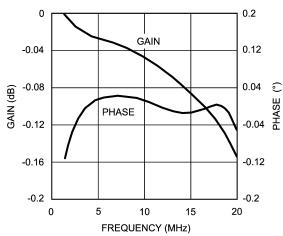

| GFL              | Gain Flatness                       | V <sub>O</sub> < 0.5V <sub>PP</sub> |                   |     |                   |         |

| GFP              | Peaking                             | DC to 200MHz                        |                   | 0.0 |                   | dB      |

| GFR              | Rolloff                             | DC to 20MHz                         |                   | .1  |                   | dB      |

| LPD              | Linear Phase Deviation              | DC to 20MHz                         |                   | .1  |                   | deg     |

| Time Dom         | ain Response                        |                                     |                   | •   | •                 |         |

| TR               | Rise and Fall Time                  | 1V Step                             |                   | 4   |                   | ns      |

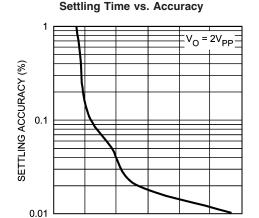

| TS               | Settling Time                       | 2V Step to 0.1%                     |                   | 12  |                   | ns      |

| OS               | Overshoot                           | 1V Step                             |                   | 1   |                   | %       |

| SR               | Slew Rate                           | 4V Step                             | 300               | 550 |                   | V/µs    |

| Distortion       | And Noise Response                  |                                     | •                 |     |                   |         |

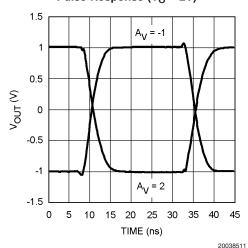

| HD2              | 2nd Harmonic Distortion             | 1V <sub>PP</sub> , 10MHz            |                   | -65 |                   | dBc     |

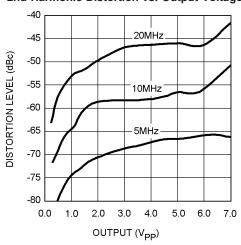

| HD3              | 3rd Harmonic Distortion             | 1V <sub>PP</sub> , 10MHz            |                   | -74 |                   | dBc     |

|                  | Equivalent Input Noise              |                                     |                   |     |                   |         |

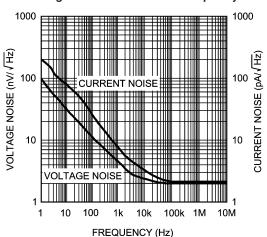

| $V_N$            | Voltage                             | 1MHz to 100MHz                      |                   | 2   |                   | nV/ √Hz |

| I <sub>N</sub>   | Current                             | 1MHz to 100MHz                      |                   | 2   |                   | pA/ √Hz |

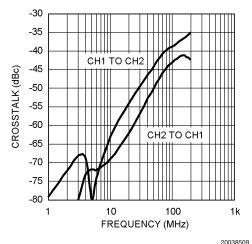

| XTLKA            | Crosstalk                           | Input Referred, 10MHz               |                   | -62 |                   | dB      |

| Static, DC       | Performance                         |                                     |                   | •   |                   |         |

| G <sub>OL</sub>  | Open-Loop Gain                      |                                     | 56<br><b>53</b>   | 63  |                   | dB      |

| V <sub>IO</sub>  | Input Offset Voltage                |                                     |                   | ±.5 | ±2<br><b>±2.6</b> | mV      |

| DV <sub>IO</sub> | Average Drift                       |                                     |                   | 5   |                   | μV/°C   |

| I <sub>BN</sub>  | Input Bias Current                  |                                     |                   | ±.7 | ±20<br><b>±30</b> | μА      |

| DI <sub>BN</sub> | Average Drift                       |                                     |                   | 150 |                   | nA/°C   |

| I <sub>os</sub>  | Input Offset Current                |                                     |                   | 0.3 | ±6                | μA      |

| I <sub>OSD</sub> | Average Drift                       |                                     |                   | 5   |                   | nA/°C   |

| PSRR             | Power Supply Rejection Ratio        |                                     | 60<br><b>46</b>   | 70  |                   | dB      |

| CMRR             | Common-Mode Rejection Ratio         |                                     | 57<br><b>54</b>   | 62  |                   | dB      |

| I <sub>cc</sub>  | Supply Current                      | Per Channel, R <sub>L</sub> = ∞     | 7.5<br><b>7.0</b> | 9   | 12<br><b>12.5</b> | mA      |

### Electrical Characteristics (Note 2) (Continued)

$V_{CC}$  = ±5V,  $A_V$  = +2V/V,  $R_F$  = 100 $\Omega$ ,  $R_G$  = 100 $\Omega$ ,  $R_L$  = 100 $\Omega$ ; unless otherwise specified. **Boldface** limits apply at the temperature extremes.

| Symbol                    | Parameter            | Conditions         | Min  | Тур  | Max | Units |  |  |

|---------------------------|----------------------|--------------------|------|------|-----|-------|--|--|

| Miscellaneous Performance |                      |                    |      |      |     |       |  |  |

| R <sub>IN</sub>           | Input Resistance     | Common-Mode        |      | 500  |     | kΩ    |  |  |

|                           |                      | Differential-Mode  |      | 200  |     | kΩ    |  |  |

| C <sub>IN</sub>           | Input Capacitance    | Common-Mode        |      | 1.5  |     | pF    |  |  |

|                           |                      | Differential-Mode  |      | 1.5  |     | pF    |  |  |

| R <sub>OUT</sub>          | Output Resistance    | Closed-Loop        |      | .1   |     | Ω     |  |  |

| Vo                        | Output Voltage Range | R <sub>L</sub> = ∞ |      | ±3.8 |     | V     |  |  |

| V <sub>OL</sub>           |                      | $R_L = 100\Omega$  | ±3.2 | ±3.5 |     | V     |  |  |

|                           |                      |                    | ±3.1 |      |     |       |  |  |

| CMIR                      | Input Voltage Range  | Common- Mode       |      | ±3.7 |     | V     |  |  |

| Io                        | Output Current       |                    | ±50  | ±85  |     | mA    |  |  |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications, see the Electrical Characteristics tables.

Note 2: Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self heating where  $T_J > T_A$ . See Note 6 for information on temperature de-rating of this device." Min/Max ratings are based on product characterization and simulation. Individual parameters are tested as noted.

Note 3: Output is short circuit protected to ground, however maximum reliability is obtained if output current does not exceed 160mA.

Note 4: Human body model,  $1.5k\Omega$  in series with 100pF. Machine model,  $0\Omega$  In series with 200pF.

Note 5: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$  and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

## **Ordering Information**

| Package    | Part Number | Package Marking | Transport Media          | NSC Drawing |

|------------|-------------|-----------------|--------------------------|-------------|

| 8-pin SOIC | LMH6628MA   | LMH6628MA       | Rails                    | M08A        |

|            | LMH6628MAX  |                 | 2.5k Units Tape and Reel | _           |

## $\textbf{Typical Performance Characteristics} \quad (T_{A} = +25^{\circ}, \ A_{V} = +2, \ V_{CC} = \pm 5V, \ R_{f} = 100\Omega, \ R_{L} = 100\Omega, \ unsuperscript{and the constraints} = 100\Omega, \ A_{V} = +200\Omega, \ A_{V}$ less specified)

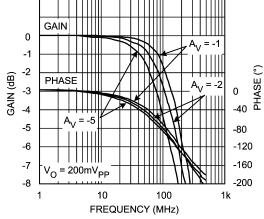

#### **Non-Inverting Frequency Response**

20038513

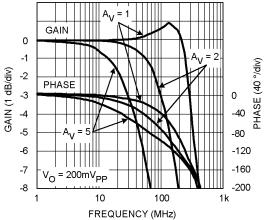

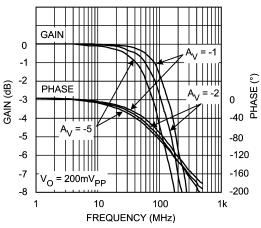

**Inverting Frequency Response**

20038515

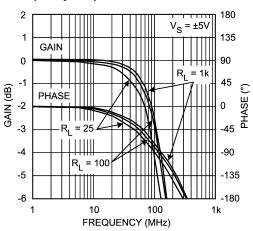

#### Frequency Response vs. Load Resistance

20038525

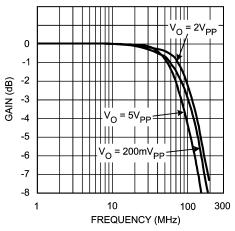

#### Frequency Response vs. Output Amplitude

20038510

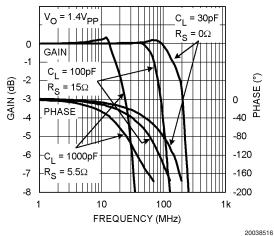

#### Frequency Response vs. Capacitive Load

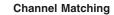

Gain Flatness & Linear Phase

20038524

## **Typical Performance Characteristics** ( $T_A$ = +25°, $A_V$ = +2, $V_{CC}$ = ±5V, $R_f$ =100 $\Omega$ , $R_L$ = 100 $\Omega$ , unless specified) (Continued)

20038514

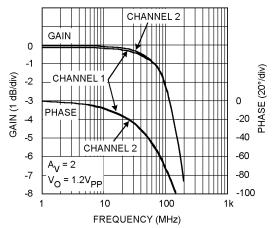

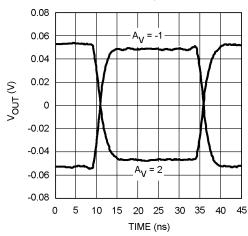

#### Pulse Response (V<sub>O</sub> = 2V)

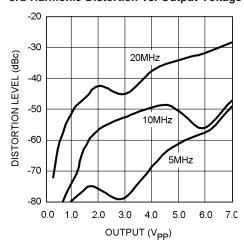

2nd Harmonic Distortion vs. Output Voltage

20038507

#### **Channel to Channel Crosstalk**

2003850

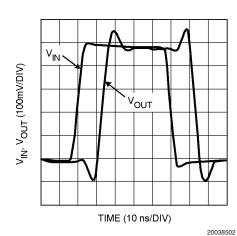

#### Pulse Response (V<sub>O</sub> = 100mV)

20038512

#### 3rd Harmonic Distortion vs. Output Voltage

20038508

# **Typical Performance Characteristics** ( $T_A = +25^{\circ}$ , $A_V = +2$ , $V_{CC} = \pm 5V$ , $R_f = 100\Omega$ , $R_L = 100\Omega$ , unless specified) (Continued)

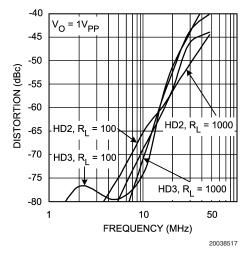

2nd & 3rd Harmonic Distortion vs. Frequency

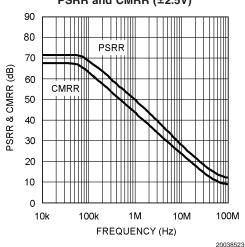

PSRR and CMRR (±2.5V)

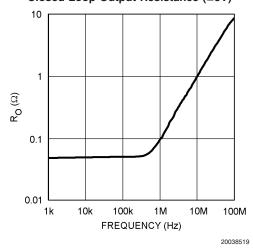

Closed Loop Output Resistance (±5V)

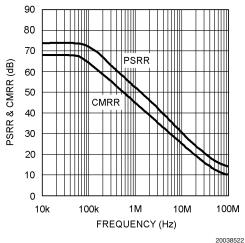

#### PSRR and CMRR (±5V)

20000322

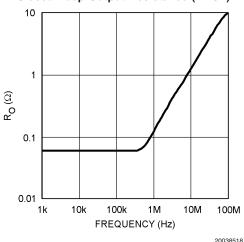

#### Closed Loop Output Resistance (±2.5V)

2003851

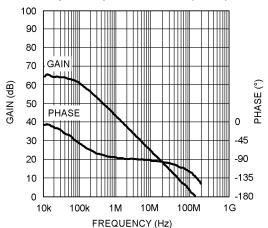

#### Open Loop Gain & Phase (±2.5V)

20038521

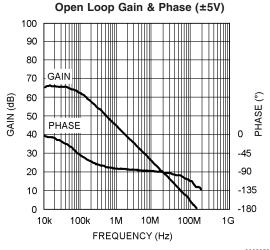

## specified) (Continued)

20038520

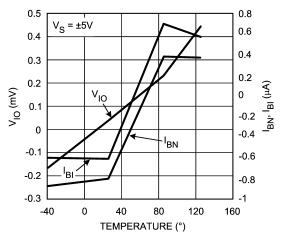

#### DC Errors vs. Temperature

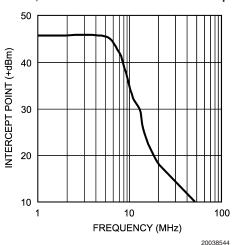

#### 2-Tone, 3rd Order Intermodulation Intercept

Recommended R<sub>S</sub> vs. C<sub>L</sub> 60 RECOMMENDED R<sub>S</sub> (Ω) 40 30 20 10 0 10 100 1000 C<sub>L</sub> (pF)

20038526

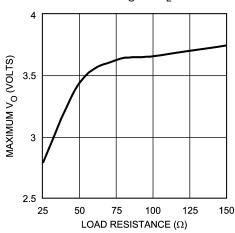

#### Maximum $V_O$ vs. $R_L$

20038545

#### Voltage & Current Noise vs. Frequency

20038547

## **Typical Performance Characteristics** ( $T_A = +25^{\circ}$ , $A_V = +2$ , $V_{CC} = \pm 5V$ , $R_f = 100\Omega$ , $R_L = 100\Omega$ , unless specified) (Continued)

5

10

15

20

TIME (ns)

25

30

35

20038548

## **Application Section**

#### **LOW NOISE DESIGN**

Ultimate low noise performance from circuit designs using the LMH6628 requires the proper selection of external resistors. By selecting appropriate low valued resistors for  $R_{\text{F}}$  and  $R_{\text{G}}$ , amplifier circuits using the LMH6628 can achieve output noise that is approximately the equivalent voltage input noise of  $2\text{nV}/\sqrt{\text{Hz}}$  multiplied by the desired gain (A\_V).

#### DC BIAS CURRENTS AND OFFSET VOLTAGES

Cancellation of the output offset voltage due to input bias currents is possible with the LMH6628. This is done by making the resistance seen from the inverting and non-inverting inputs equal. Once done, the residual output offset voltage will be the input offset voltage ( $V_{OS}$ ) multiplied by the desired gain ( $A_{V}$ ). National Application Note OA-7 offers several solutions to further reduce the output offset.

#### **OUTPUT AND SUPPLY CONSIDERATIONS**

With  $\pm 5\text{V}$  supplies, the LMH6628 is capable of a typical output swing of  $\pm 3.8\text{V}$  under a no-load condition. Additional output swing is possible with slightly higher supply voltages. For loads of less than  $50\Omega$ , the output swing will be limited by the LMH6628's output current capability, typically 85mA.

Output settling time when driving capacitive loads can be improved by the use of a series output resistor. See the plot labeled "R $_{\rm S}$  vs. C $_{\rm L}$ " in the Typical Performance section.

#### LAYOUT

Proper power supply bypassing is critical to insure good high frequency performance and low noise. De-coupling capacitors of  $0.1\mu F$  should be placed as close as possible to the power supply pins. The use of surface mounted capacitors is recommended due to their low series inductance.

A good high frequency layout will keep power supply and ground traces away from the inverting input and output pins. Parasitic capacitance from these nodes to ground causes frequency response peaking and possible circuit oscillation.

See OA-15 for more information. National suggests the 730036 (SOIC) dual op amp evaluation board as a guide for high frequency layout and as an aid in device evaluation.

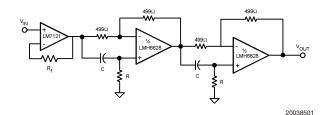

#### ANALOG DELAY CIRCUIT (ALL-PASS NETWORK)

The circuit in *Figure 1* implements an all-pass network using the LMH6628. A wide bandwidth buffer (LM7121) drives the circuit and provides a high input impedance for the source. As shown in *Figure 2*, the circuit provides a 13.1ns delay (with R =  $40.2\Omega$ , C = 47pF). R<sub>F</sub> and R<sub>G</sub> should be of equal and low value for parasitic insensitive operation.

FIGURE 1.

FIGURE 2. Delay Circuit Response to 0.5V Pulse

## Application Section (Continued)

The circuit gain is +1 and the delay is determined by the following equations.

$$^{\tau}$$

delay = 2(2RC +  $^{\tau}$ d) (1)

$$T_{d} = \frac{1}{360} \frac{d\phi}{df};$$

(2)

where  $T_d$  is the delay of the op amp at  $A_V = +1$ .

The LMH6628 provides a typical delay of 2.8ns at its -3dB point.

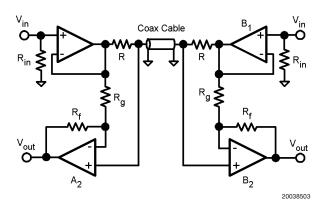

#### **FULL DUPLEX DIGITAL OR ANALOG TRANSMISSION**

Simultaneous transmission and reception of analog or digital signals over a single coaxial cable or twisted-pair line can reduce cabling requirements. The LMH6628's wide bandwidth and high common-mode rejection in a differential amplifier configuration allows full duplex transmission of video, telephone, control and audio signals.

In the circuit shown in *Figure 3*, one of the LMH6628's amps is used as a "driver" and the other as a difference "receiver" amplifier. The output impedance of the "driver" is essentially zero. The two R's are chosen to match the characteristic impedance of the transmission line. The "driver" op amp gain can be selected for unity or greater.

Receiver amplifier  $A_2$  ( $B_2$ ) is connected across R and forms differential amplifier for the signals transmitted by driver  $A_2$  ( $B_2$ ). If  $R_F$  equals  $R_G$ , receiver  $A_2$  ( $B_1$ ) will then reject the signals from driver  $A_1$  ( $B_1$ ) and pass the signals from driver  $B_1$  ( $A_1$ ).

FIGURE 3.

The output of the receiver amplifier will be:

$$V_{\text{out}}_{A(B)} = \frac{1}{2} V_{\text{in}}_{A(B)} \left[ 1 - \frac{R_f}{R_g} \right] + \frac{1}{2} V_{\text{in}}_{B(A)} \left[ 1 + \frac{R_f}{R_g} \right]$$

(3)

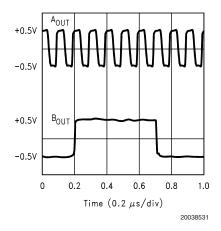

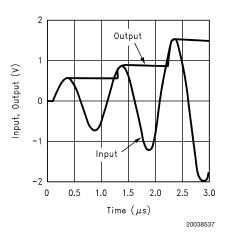

Care must be given to layout and component placement to maintain a high frequency common-mode rejection. The plot of *Figure 4* shows the simultaneous reception of signals transmitted at 1MHz and 10MHz.

FIGURE 4.

#### POSITIVE PEAK DETECTOR

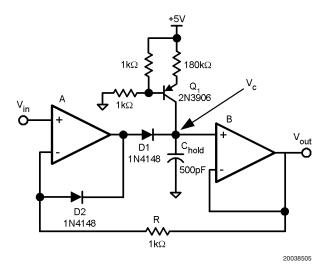

The LMH6628's dual amplifiers can be used to implement a unity-gain peak detector circuit as shown in *Figure 5*.

FIGURE 5.

The acquisition speed of this circuit is limited by the dynamic resistance of the diode when charging  $C_{\text{hold}}$ . A plot of the circuit's performance is shown in *Figure 6* with a 1MHz sinusoidal input.

## **Application Section** (Continued)

#### FIGURE 6.

A current source, built around Q1, provides the necessary bias current for the second amplifier and prevents saturation when power is applied. The resistor, R, closes the loop while diode D2 prevents negative saturation when  $V_{\rm IN}$  is less than  $V_{\rm C}$ . A MOS-type switch (not shown) can be used to reset the capacitor's voltage.

The maximum speed of detection is limited by the delay of the op amps and the diodes. The use of Schottky diodes will provide faster response.

#### ADJUSTABLE OR BANDPASS EQUALIZER

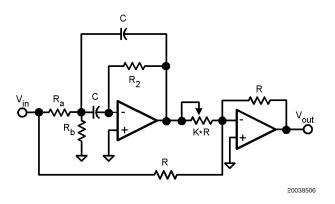

A "boost" equalizer can be made with the LMH6628 by summing a bandpass response with the input signal, as shown in *Figure 7*.

FIGURE 7.

The overall transfer function is shown in Eq. 5.

$$\frac{V_{\text{out}}}{V_{\text{in}}} = \left[\frac{R_{\text{b}}}{K(R_{\text{a}} + R_{\text{b}})}\right] \frac{s2Q\omega_{\text{o}}}{s^2 + s\frac{\omega_{\text{o}}}{Q} + \omega_{\text{o}}^2} - 1$$

(4)

To build a boost circuit, use the design equations Eq. 6 and Eq. 7.

$$\frac{R_2C}{2} = \frac{Q}{\omega_o}$$

$$2C (R_a||R_b) = \frac{1}{Q\omega_o}$$

(5)

(6)

Select  $R_2$  and C using Eq. 6. Use reasonable values for high frequency circuits -  $R_2$  between  $10\Omega$  and  $5k\Omega$ , C between 10pF and 2000pF. Use Eq. 7 to determine the parallel combination of  $R_a$  and  $R_b$ . Select  $R_a$  and  $R_b$  by either the  $10\Omega$  to  $5k\Omega$  criteria or by other requirements based on the impedance  $V_{\rm in}$  is capable of driving. Finish the design by determining the value of K from Eq. 8.

Peak Gain =

$$\frac{V_{out}}{V_{in}} (\omega_o) = \frac{R_2}{2KR_a} - 1$$

(7)

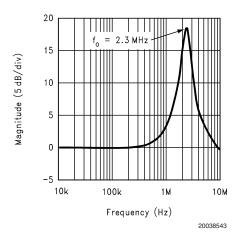

Figure 8 shows an example of the response of the circuit of Figure 9, where  $f_o$  is 2.3MHz. The component values are as follows:  $R_a$ =2.1k $\Omega$ ,  $R_b$  = 68.5 $\Omega$ ,  $R_2$  = 4.22k $\Omega$ , R = 500 $\Omega$ , KR = 50 $\Omega$ , C = 120pF.

FIGURE 8.

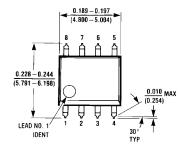

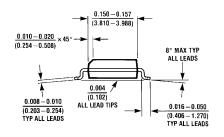

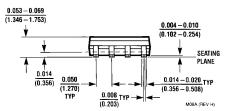

### Physical Dimensions inches (millimeters)

unless otherwise noted

8-Pin SOIC NS Package Number M08A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560